Vishay Siliconix

## **Power MOSFET**

| PRODUCT SUMMARY                 |                          |      |  |  |

|---------------------------------|--------------------------|------|--|--|

| V <sub>DS</sub> (V)             | 100                      |      |  |  |

| $R_{DS(on)}\left(\Omega\right)$ | $V_{GS} = 5.0 \text{ V}$ | 0.54 |  |  |

| Q <sub>g</sub> (Max.) (nC)      | 6.1                      |      |  |  |

| Q <sub>gs</sub> (nC)            | 2.6                      |      |  |  |

| Q <sub>gd</sub> (nC)            | 3.3                      |      |  |  |

| Configuration                   | Single                   |      |  |  |

#### **FEATURES**

- Dynamic dV/dt Rating

- Repetitive Avalanche Rated

- For Automatic Insertion

- End Stackable

- · Logic-Level Gate Drive

- R<sub>DS(on)</sub> Specified at V<sub>GS</sub> = 4 V and 5 V

- 175 °C Operating Temperature

- Lead (Pb)-free Available

#### **DESCRIPTION**

Third generation Power MOSFETs from Vishay provide the designer with the best combination of fast switching, ruggedized device design, low on-resistance and cost-effectiveness.

The 4 pin DIP package is a low cost machine-insertable case style which can be stacked in multiple combinations on standard 0.1" pin centers. The dual drain serves as a thermal link to the mounting surface for power dissipation levels up to 1 W.

| ORDERING INFORMATION |             |  |

|----------------------|-------------|--|

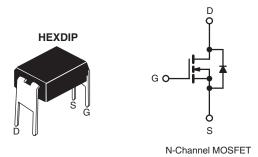

| Package              | HEXDIP      |  |

| Load (Dh.) free      | IRLD110PbF  |  |

| Lead (Pb)-free       | SiHLD110-E3 |  |

| SnPb                 | IRLD110     |  |

|                      | SiHLD110    |  |

| ABSOLUTE MAXIMUM RATINGS T                       | <sub>C</sub> = 25 °C, u  | nless otherw            | rise noted                        |                  |      |  |

|--------------------------------------------------|--------------------------|-------------------------|-----------------------------------|------------------|------|--|

| PARAMETER                                        |                          |                         | SYMBOL                            | LIMIT            | UNIT |  |

| Drain-Source Voltage                             |                          |                         | $V_{DS}$                          | 100              | V    |  |

| Gate-Source Voltage                              |                          |                         | $V_{GS}$                          | ± 10             | 7 V  |  |

| Continuous Drain Current                         | V <sub>GS</sub> at 5.0 V | T <sub>C</sub> = 25 °C  | - I <sub>D</sub>                  | 1.0              | А    |  |

|                                                  |                          | T <sub>C</sub> = 100 °C |                                   | 0.70             |      |  |

| Pulsed Drain Current <sup>a</sup>                |                          |                         | I <sub>DM</sub>                   | 8.0              | 1    |  |

| Linear Derating Factor                           |                          |                         |                                   | 0.0083           | W/°C |  |

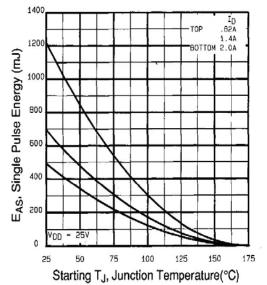

| Single Pulse Avalanche Energy <sup>b</sup>       |                          |                         | E <sub>AS</sub>                   | 490              | mJ   |  |

| Avalanche current <sup>a</sup>                   |                          |                         | I <sub>AR</sub>                   | 1.0              | Α    |  |

| Repetitive Avalanche Energy <sup>a</sup>         |                          |                         | E <sub>AR</sub>                   | 0.13             | mJ   |  |

| Maximum Power Dissipation                        | T <sub>C</sub> = 25 °C   |                         | P <sub>D</sub>                    | 1.3              | W    |  |

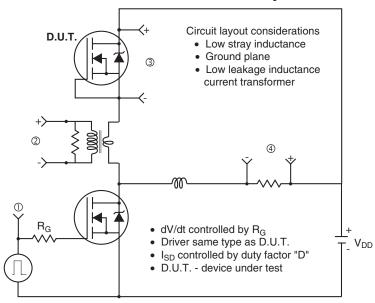

| Peak Diode Recovery dV/dt <sup>c</sup>           |                          |                         | dV/dt                             | 5.5              | V/ns |  |

| Operating Junction and Storage Temperature Range |                          |                         | T <sub>J</sub> , T <sub>stg</sub> | - 55 to + 175    | °C   |  |

| Soldering Recommendations (Peak Temperature)     | for 10 s                 |                         |                                   | 300 <sup>d</sup> |      |  |

#### Notes

- a. Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).

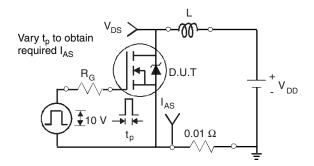

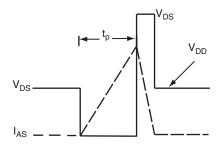

- b.  $V_{DD}$  = 25 V, starting  $T_J$  = 25 °C, L = 183 mH,  $R_G$  = 25  $\Omega$ ,  $I_{AS}$  = 2.0 A (see fig. 12).

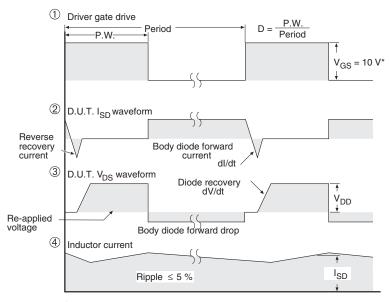

- c.  $I_{SD} \leq 5.6$  A,  $dI/dt \leq 75$  A/ $\mu$ s,  $V_{DD} \leq V_{DS}$ ,  $T_J \leq 175$  °C.

- d. 1.6 mm from case.

<sup>\*</sup> Pb containing terminations are not RoHS compliant, exemptions may apply

# IRLD110, SiHLD110

# Vishay Siliconix

| THERMAL RESISTANCE RATINGS  |            |      |      |      |  |

|-----------------------------|------------|------|------|------|--|

| PARAMETER                   | SYMBOL     | TYP. | MAX. | UNIT |  |

| Maximum Junction-to-Ambient | $R_{thJA}$ | =    | 120  | °C/W |  |

| PARAMETER                                 | SYMBOL                | TES                                                                                                       | MIN.                                                                            | TYP.      | MAX.                   | UNIT  |      |  |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------|------------------------|-------|------|--|

| Static                                    |                       |                                                                                                           |                                                                                 |           |                        |       |      |  |

| Drain-Source Breakdown Voltage            | V <sub>DS</sub>       | V <sub>GS</sub> =                                                                                         | 100                                                                             | -         | -                      | V     |      |  |

| V <sub>DS</sub> Temperature Coefficient   | $\Delta V_{DS}/T_{J}$ | Reference                                                                                                 | Reference to 25 °C, I <sub>D</sub> = 1 mA                                       |           |                        | -     | V/°C |  |

| Gate-Source Threshold Voltage             | V <sub>GS(th)</sub>   | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 250 μA                                               |                                                                                 | 1.0       | -                      | 2.0   | V    |  |

| Gate-Source Leakage                       | I <sub>GSS</sub>      | V <sub>GS</sub> = ± 10 V                                                                                  |                                                                                 | -         | -                      | ± 100 | nA   |  |

| Zana Oata Wallana Busin Oamani            |                       | V <sub>DS</sub> =                                                                                         | V <sub>DS</sub> = 100 V, V <sub>GS</sub> = 0 V                                  |           | -                      | 25    |      |  |

| Zero Gate Voltage Drain Current           | I <sub>DSS</sub>      | V <sub>DS</sub> = 80 V                                                                                    | V <sub>GS</sub> = 0 V, T <sub>J</sub> = 150 °C                                  | -         | -                      | 250   | μΑ   |  |

| Dunin Course On Chata Basistana           | Ъ                     | V <sub>GS</sub> = 5.0 V                                                                                   | I <sub>D</sub> = 0.60 A <sup>b</sup>                                            | -         | -                      | 0.54  |      |  |

| Drain-Source On-State Resistance          | R <sub>DS(on)</sub>   | V <sub>GS</sub> = 4.0 V                                                                                   | I <sub>D</sub> = 0.50 A <sup>b</sup>                                            | -         | -                      | 0.76  | Ω    |  |

| Forward Transconductance                  | 9 <sub>fs</sub>       | V <sub>DS</sub> = 50 V, I <sub>D</sub> = 0.60 A <sup>b</sup>                                              |                                                                                 | 1.3       | -                      | -     | S    |  |

| Dynamic                                   |                       |                                                                                                           |                                                                                 | •         | •                      | •     | ,    |  |

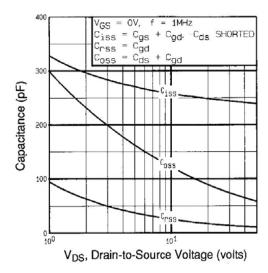

| Input Capacitance                         | C <sub>iss</sub>      | $V_{GS} = 0 V$                                                                                            |                                                                                 | -         | 250                    | -     | pF   |  |

| Output Capacitance                        | C <sub>oss</sub>      |                                                                                                           | $V_{DS} = 25 V$                                                                 |           | 80                     | -     |      |  |

| Reverse Transfer Capacitance              | C <sub>rss</sub>      | $f = 1.0 \overline{MHz}$ , see fig. 5                                                                     |                                                                                 | -         | 15                     | -     |      |  |

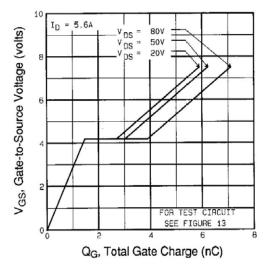

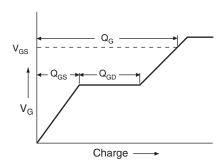

| Total Gate Charge                         | Qg                    |                                                                                                           |                                                                                 | -         | -                      | 6.1   | nC   |  |

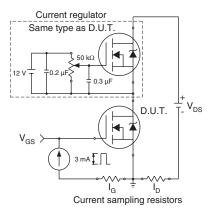

| Gate-Source Charge                        | Q <sub>gs</sub>       | V <sub>GS</sub> = 5.0 V                                                                                   | $I_D = 5.6 \text{ A}, V_{DS} = 80 \text{ V},$<br>see fig. 6 and 13 <sup>b</sup> | -         | -                      | 2.6   |      |  |

| Gate-Drain Charge                         | Q <sub>gd</sub>       |                                                                                                           | See lig. o allu 13-                                                             | -         | -                      | 3.3   |      |  |

| Turn-On Delay Time                        | t <sub>d(on)</sub>    |                                                                                                           |                                                                                 | -         | 9.3                    | -     |      |  |

| Rise Time                                 | t <sub>r</sub>        | T                                                                                                         | - 50 V I 5 6 A                                                                  | -         | 4.7                    | -     | 1    |  |

| Turn-Off Delay Time                       | t <sub>d(off)</sub>   | $V_{DD} = 50 \text{ V}, I_D = 5.6 \text{ A},$ $R_G = 12 \Omega, R_D = 8.4 \Omega, \text{ see fig. } 10^b$ |                                                                                 | -         | 16                     | -     | - ns |  |

| Fall Time                                 | t <sub>f</sub>        |                                                                                                           |                                                                                 | -         | 17                     | -     |      |  |

| Internal Drain Inductance                 | L <sub>D</sub>        | Between lead,<br>6 mm (0.25") from<br>package and center of<br>die contact                                |                                                                                 | -         | 4.0                    | -     | - nH |  |

| Internal Source Inductance                | L <sub>S</sub>        |                                                                                                           |                                                                                 | -         | 6.0                    | -     |      |  |

| Drain-Source Body Diode Characteristic    | s                     | 1                                                                                                         |                                                                                 |           |                        |       |      |  |

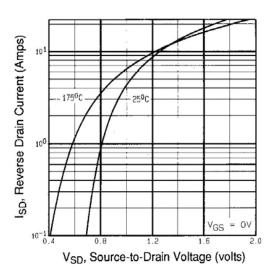

| Continuous Source-Drain Diode Current     | Is                    | MOSFET sym                                                                                                | MOSFET symbol showing the                                                       |           | -                      | 1.0   | - A  |  |

| Pulsed Diode Forward Current <sup>a</sup> | I <sub>SM</sub>       | integral reverse p - n junction diode                                                                     |                                                                                 | -         | -                      | 8.0   |      |  |

| Body Diode Voltage                        | V <sub>SD</sub>       | T <sub>J</sub> = 25 °C, I <sub>S</sub> = 1.0 A, V <sub>GS</sub> = 0 V <sup>b</sup>                        |                                                                                 | -         | -                      | 2.5   | V    |  |

| Body Diode Reverse Recovery Time          | t <sub>rr</sub>       | $T_J = 25 \text{ °C}, I_F = 5.6 \text{ A, dl/dt} = 100 \text{ A/}\mu\text{s}^b$                           |                                                                                 | -         | 110                    | 130   | ns   |  |

| Body Diode Reverse Recovery Charge        | Q <sub>rr</sub>       |                                                                                                           |                                                                                 | -         | 0.50                   | 0.65  | μC   |  |

| Forward Turn-On Time                      | t <sub>on</sub>       | Intrinsic tu                                                                                              | on is don                                                                       | ninated b | y L <sub>S</sub> and I | _D)   |      |  |

#### Notes

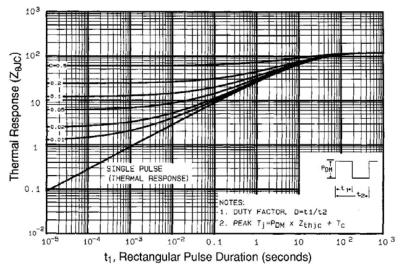

- a. Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11).

- b. Pulse width  $\leq$  300 µs; duty cycle  $\leq$  2 %.

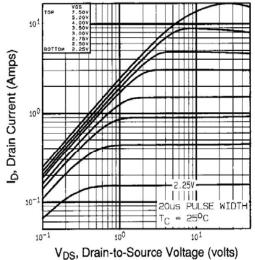

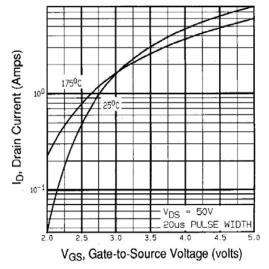

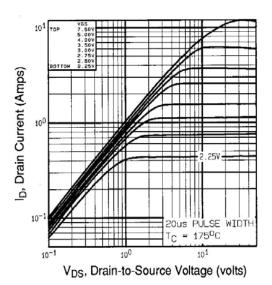

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

Fig. 1 - Typical Output Characteristics,  $T_C = 25$  °C

Fig. 3 - Typical Transfer Characteristics

Fig. 2 - Typical Output Characteristics,  $T_C = 175$  °C

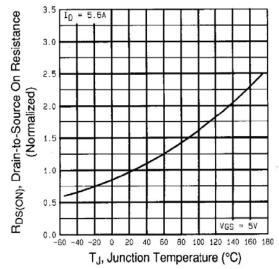

Fig. 4 - Normalized On-Resistance vs. Temperature

# Vishay Siliconix

Fig. 5 - Typical Capacitance vs. Drain-to-Source Voltage

Fig. 7 - Typical Source-Drain Diode Forward Voltage

Fig. 6 - Typical Gate Charge vs. Gate-to-Source Voltage

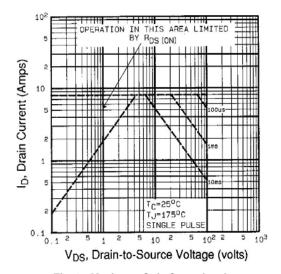

Fig. 8 - Maximum Safe Operating Area

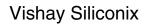

Fig. 9 - Maximum Drain Current vs. Case Temperature

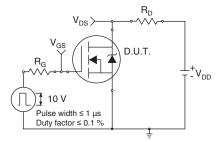

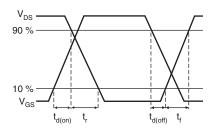

Fig. 10a - Switching Time Test Circuit

Fig. 10b - Switching Time Waveforms

Fig. 11 - Maximum Effective Transient Thermal Impedance, Junction-to-Case

# Vishay Siliconix

Fig. 12a - Unclamped Inductive Test Circuit

Fig. 12b - Unclamped Inductive Waveforms

Fig. 12c - Maximum Avalanche Energy vs. Drain Current

Fig. 13a - Basic Gate Charge Waveform

Fig. 13b - Gate Charge Test Circuit

### Peak Diode Recovery dV/dt Test Circuit

\*  $V_{GS} = 5 V$  for logic level devices

Fig. 14 - For N-Channel

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?91309.

Vishay

### **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com